Goal

- 명령어 파이프라인 구조에 대한 이해

- 명령어 파이프라인 발전 흐름에 대한 이해(구조적 문제점 및 등장 배경의 기초적인 이해)

명령어 파이프라인

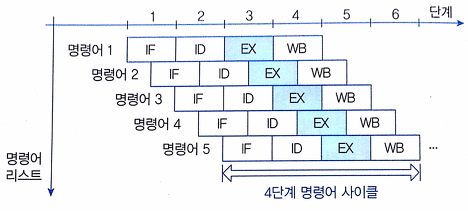

CPU 처리성능 향상을 위해 Instruction 처리 과정을 여러 단계로 세분화하는 병렬처리 기법

파이프라인 발전 단계

파이프라인의 유형

T: 명령어 실행 시간, k: 파이프라인 단계, N 실행 명령어 수

- 명령어 인출(IF, Instruction fetch)

- 명령어 해독(ID, Instruction Decode)

- 연산 실행(EX, EXecution)

- 연산결과 저장(WB, Write Back)

파이프라인(pipeline)

특징

- Micro Instruction 기반 병렬처리

- 성능 : Pt = k + (N – 1)

슈퍼 파이프라인(super-pipeline)

특징

- 파이프라인 단계수는 유지하면서 각 단계 내에서 처리속도를 몇 배로 높여주는 CPU 설계 기술

- 계산 유형 : CPU Clock Degree 기반 파이프라인

- 성능 : SPt = k + 1/n * (N – 1)

- n: CPU Clock degree (1 Clock 당 수행 횟수)

- n값이 커질수록 수행 시간은 줄어든다.

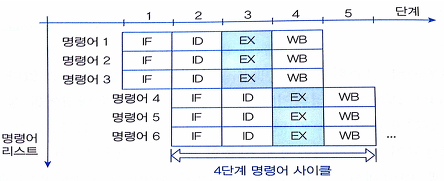

슈퍼 스칼라(superscala)

- CPU 내에 파이프라인을 여러 개 두어(중첩) 여러 명령어를 동시에 실행하는 기술

- 여러 개의 명령어 인출 장치, 실행 장치들이 필요

- 동시에 실행되어도 무관한 독립적인 명령어들을 판단해 골라내는 장치 필요

- 성능 : SSt = k + (N – m)/m

- m : 파이프라인 중첩 수

슈퍼 파이프라인 슈퍼 스칼라(spuer-piped superscala)

- 슈퍼 파이프라인 + 슈퍼 스칼라

- 성능 : SPSSt = k + (N – m)/(m * n)

VLIW(Very Long Instruction Word)

<참고>

CISC, RISC, VIEW, EPIC 관련 내용을 정리한 자료

CISC(Complex instruction set computer)

- 간단한 명령어 부터 복잡한 명령어까지 다양하게 존재

- 명령어에 따라 명령어 길이도 제각각

- 복잡한 기계어 명령까지 모두 고려해야 하므로 명령어 실행 단계가 많아지고 설계가 복잡해짐

- 또한, 명령어에 따라 수행에 필요한 클럭 개수도 제각각 다르다.

위와 같은 이유로 RISC가 등장하게 되었다. (RISC 등장 배경)

RISC(Reduced Instruction Set Computer)

- 많이 사용되는 명령어들의 대부분이 간단한 명령어라는 것에 착안하여 복잡한 명령어를 없앰

- 이론적으로 한 클럭에 한 명령어가 처리되도록 설계

- 명령어 크기가 일정

- 범용 레지스터의 개수를 대폭 늘려 메모리 접근 횟수를 최소화(많은 레지스터 필요)

- 하드웨어 설계에 유리 : CISC에 비해 회로가 덜 복잡해 병렬처리 CPU를 설계하는데 효율적

- 프로그램 설계에 유리 : 적은 수의 명령어(종류)를 조합해 프로그램 설계 가능

RISC의 한계와 VLIW 의 등장

명령어 종류를 줄이는 방식으로 CPU 성능을 향상 시키는 것에는 한계가 있다.

컴파일러에 의해 전달받은 명령어들을 적절히 배치해 병렬 처리를 해야 하는데, 이때 상당한 하드웨어 자원 낭비가 발생한다. 그래서 그 해결책 중 하나로 등장한 것이 VLIW 구조이다.

VLIW 구조는 컴파일러가 직접 명령어 병렬처리에 관여할 수 있도록 한다.

처음부터 디코드 유닛에 한꺼번에 종속성이 없는 여러 명령어를 때려박고 그걸 한번에 처리하여 효율성을 높이는 방식이다.

CISC, RISC, VIEW, EPIC 관련 내용을 정리한 자료

CISC(Complex instruction set computer)

- 간단한 명령어 부터 복잡한 명령어까지 다양하게 존재

- 명령어에 따라 명령어 길이도 제각각

- 복잡한 기계어 명령까지 모두 고려해야 하므로 명령어 실행 단계가 많아지고 설계가 복잡해짐

- 또한, 명령어에 따라 수행에 필요한 클럭 개수도 제각각 다르다.

위와 같은 이유로 RISC가 등장하게 되었다. (RISC 등장 배경)

RISC(Reduced Instruction Set Computer)

- 많이 사용되는 명령어들의 대부분이 간단한 명령어라는 것에 착안하여 복잡한 명령어를 없앰

- 이론적으로 한 클럭에 한 명령어가 처리되도록 설계

- 명령어 크기가 일정

- 범용 레지스터의 개수를 대폭 늘려 메모리 접근 횟수를 최소화(많은 레지스터 필요)

- 하드웨어 설계에 유리 : CISC에 비해 회로가 덜 복잡해 병렬처리 CPU를 설계하는데 효율적

- 프로그램 설계에 유리 : 적은 수의 명령어(종류)를 조합해 프로그램 설계 가능

RISC의 한계와 VLIW 의 등장

명령어 종류를 줄이는 방식으로 CPU 성능을 향상 시키는 것에는 한계가 있다.

컴파일러에 의해 전달받은 명령어들을 적절히 배치해 병렬 처리를 해야 하는데, 이때 상당한 하드웨어 자원 낭비가 발생한다. 그래서 그 해결책 중 하나로 등장한 것이 VLIW 구조이다.

VLIW 구조는 컴파일러가 직접 명령어 병렬처리에 관여할 수 있도록 한다.

처음부터 디코드 유닛에 한꺼번에 종속성이 없는 여러 명령어를 때려박고 그걸 한번에 처리하여 효율성을 높이는 방식이다.

- 긴 명령어 하나에 여러개의 연산을 포함시켜 내보내는 구조

- CPU로 명령어를 보내기 전에 병렬 처리 가능한 명령어들을 컴파일러가 미리 판단

- 동시에 실행될 수 있는 연산을 가진 명령어들을 하나로 묶어 긴 명령어 형식 내에 재배열한다.

- 정교한 컴파일러 기술이 필요 (하드웨어 구조는 간단해 졌지만, 컴파일러가 복잡해짐)

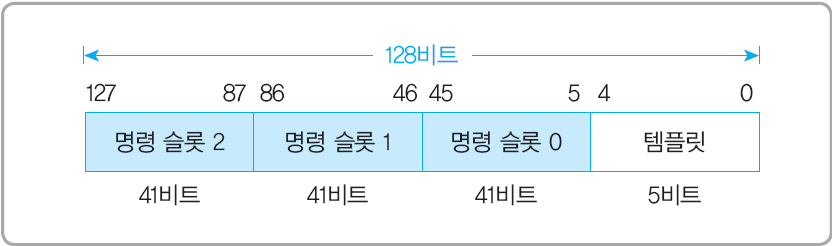

EPIC(Explicit Parallel Instruction Computing)

(IA-64 명령어 구조라고도 함. instruction architecture - 64)

- VLIW의 일종이다.

- 128bit 길이의 명령어 형식

- 5bit template : 32개의 템플릿 제공으로 호환성 향상 (실행 방법)

- 3개의 41bit 명령 슬롯

파이프라인 해저드(hazard)

명령어 실행 지속이 불가하여 지정된 클럭에서 수행되는 파이프라인이 지연, 중지되는 현상

파이프라인에서 자원 충돌, 명령어 의존성 등에 의해 해저드(hazard)가 발생할 수 있기 때문에, 파이프라인의 단계수를 늘리거나 중첩시킨다고 해서 무한정 성능이 향상 되지는 않는다.

같이 보면 좋은 참고 사이트

- 해저드(hazard)

- 분기 예측

<참고>

References

'운영체제' 카테고리의 다른 글

| 메모리(memory) (0) | 2020.10.06 |

|---|---|

| 중앙처리장치(CPU) - 5 (병렬 컴퓨팅, 병렬 컴퓨터) (0) | 2020.09.30 |

| 중앙처리장치(CPU) - 3 (CPU 명령어 사이클) (0) | 2020.09.21 |

| 중앙처리장치(CPU) - 2 (CPU 명령어) (0) | 2020.09.21 |

| 중앙처리장치(CPU) - 1 (CPU 구조) (0) | 2020.09.20 |